2025年12月23日

次世代半導体に向けた有機インターポーザ開発用TEGの開発

研究期間:令和6年4月〜令和7年3月

実施場所:海老名本部

研究担当:電子技術部 電子デバイスグループ

研究概要

1.背景

近年、半導体分野において、設計コストの増大に対応するため、デバイスを積層し高性能化を可能とする3次元や2.5次元積層実装が行われ、使用される伝送路についても高周波化(10GHz)が求められています。そのため、高周波化に対応する低誘電率、低誘電正接である有機材料が注目されており、CPU-メモリ間を繋ぐインターポーザへの適用が望まれています。また、国内には材料・装置メーカーが複数存在しますが、評価用TEG(Test Element Group)の調達は容易ではなく、簡易に利用できるTEGの研究開発も求められています。

そこで、次世代半導体に向けた有機インターポーザ開発用TEGの実現を目指し、KISTECと東京都市大学が共同で、本事業を実施しました。

研究成果と今後の取組

2.実施内容

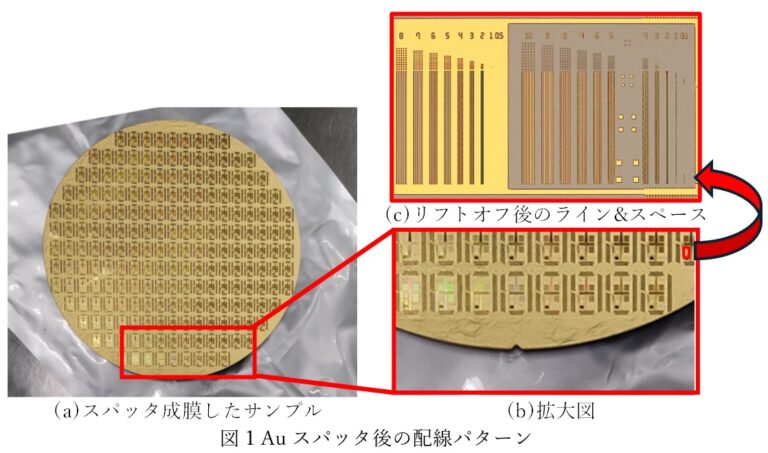

まず、樹脂材と金属薄膜の密着性を確認するため、既存フォトマスクを利用し、スパッタ法によるプロセス確認を実施しました(図1 (a))。その結果Si上への配線形成では剥離が発生せず、レジスト上の配線形成では剥離が発生することが分かりました(図1 (b))。この問題に対しては、今後、配線作製プロセスの見直しを含め、対応していく予定です。

また、Si上の配線形成状態についてリフトオフを実施し、ライン&スペースを確認した結果、3μm幅まで作製可能なことがわかりました(図1 (c))。

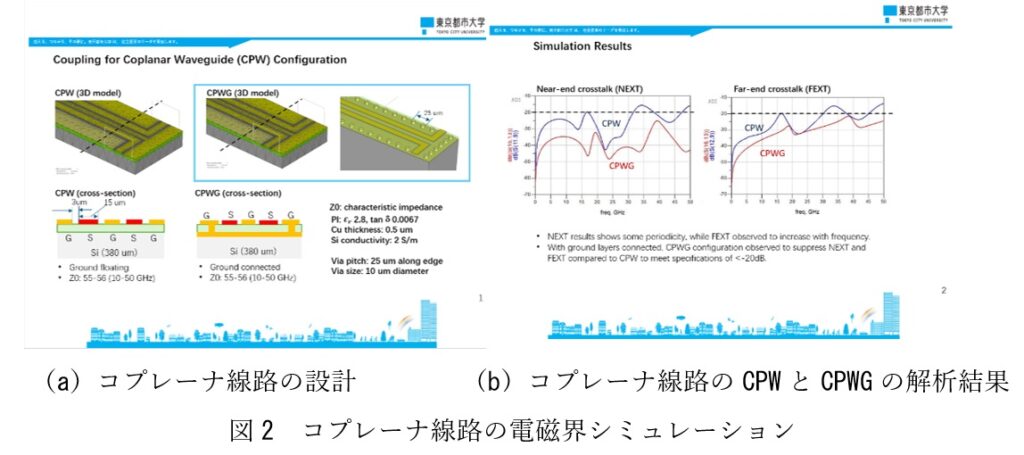

一方、東京都市大学においては、コプレーナ線路のクロストーク評価を電磁界シミュレーションにより実施しました(図2)。ここでは、配線幅15μm、配線長 1mmとしノイズの影響を最大にするため、実際の配線形成で最小線幅であった3μm、18μmピッチでCPW(コプレーナ線路)とCPWG(グランド付きコプレーナ線路)の比較を行っています。その結果、周波数10GHzまでの範囲では、一般的なCPWGを使用し20μmから55μmピッチ、クロストーク20dB以下が実現できることが分かりました。

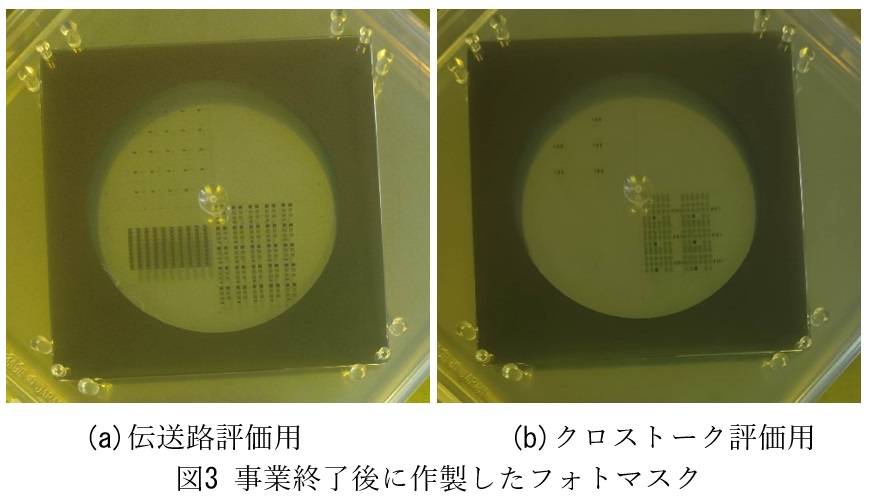

最後に、有機インターポーザ作製のため、電気特性評価を実施可能なフォトマスクの設計を行いました。その際、半導体関連企業と打ち合わせ結果を踏まえ、初期の15μm線幅に加えて、より微細な数μmの幅の配線パターンを追加しています。

3.成果の展開

本事業終了後、作製したフォトマスクを図3に示します。このフォトマスクには伝送路とクロストーク評価用のパターンを有しており、材料を提供いただき、配線を形成することで電気特性評価を行うことが可能です。

その他

この事業はKEIRINの補助を受け実施しました。

※KEIRIN公式HP(別サイト)へリンクいたします。